WInnComm Europe 2016 Papers and Presentations

11-12 October 2016

Paris, France

Tuesday, 11 October 2016

Tactical Communications 1 - Nations' Perspectives (download presentations here)

Session Chair: David Renaudau (Thales)

- Wireless Technologies for the C41 Battlefield Transformation

Philippe Marguerie (Thales) - SVFuA - The German SDR Program

- Roland Kowald (BAAINBw)

-

- UK - Perspective on Tactical Communications

- George Vongas (DSTL)

-

- ESSOR HDRWF Secure Coalition Waveform Verification Achievements

-

Charles Chedhomme (ESSOR) and Christian Serra (A4ESSOR)

This paper presents the system level verification achievements of the ESSOR High Data Rate Waveform (ESSOR HDRWF) in a coalition environment. The ESSOR HDRWF is an innovative coalition secure high data rate mobile ad-hoc networking waveform for land military applications, brigade and below. The ESSOR HDRWF has been elaborated in the scope of the European Secure Software defined Radio (ESSOR) program, a major Software Defined Radio (SDR) program sponsored by the governments of Finland, France, Italy, Poland, Spain and Sweden, and awarded by the Organisation Conjointe de Coopération en matière d'ARmement (OCCAR) to the dedicated joint venture Alliance for ESSOR (a4ESSOR) in charge of managing the consortium composed of the following respective National Champions: Bittium, Indra, Radmor, Saab, Finmeccanica and Thales Communications & Security. The ESSOR HDRWF has been developed as a shared and portable SDR waveform application (WFA), the HDR Base WF. This WFA has been ported and validated on heterogeneous SDR platforms from different ESSOR nations. Interoperability between these national SDR platforms, using the ported WFA, has also been demonstrated through successful interoperability qualification activities, based on various scenarios. This paper presents the main features, capabilities and performances of the ESSOR HDRWF. Special emphasis is put on the HDRWF innovative features, addressing the capabilities to efficiently handle synchronization in absence of common time reference (i.e.: GNSS); to properly manage communication on the move; to dynamically adapt to the operational environment; to be able to scale from sparse networks with few nodes up to dense networks with a high number of nodes. A specific insight is provided on the military grade embedded security features making it suitable for its usage in harsh environments, such as the tactical battlefield. Moreover, this paper focuses on the different levels of system verification activities performed nationally and multi-nationally through interoperability tests amongst the various national heterogeneous SDR platforms. The categorization of interoperability verification scenarios is presented along with the achieved performances matching the presented main capabilities. Finally this paper presents the future evolutions of the HDRWF currently in preparation.

Wireless Technologies - Building the 5G Evolution 1 (download presentations here)

Session Chair: Claude Belisle (NordiaSoft)

IoT for eHealth - Friend or Foe?-

Stephen R Hope (Docobo Ltd UK)

The concept of the internet of Things is something that is suddenly at the forefront of next generation technologies with the idea of billions of connected sensors providing a rich source of data for our everyday lives. This vision has now extended to the eHealth domain on the basis that this myriad of sensors will give indications about the health and wellbeing of a patient which will be used to make a diagnosis of the patient's condition by the clinician. Yet within the mountain of data the question has to be asked how much INFORMATION can be distilled that can actually be used by the clinician to care for an individual patient, i.e small data not big data methodologies whilst still meeting Information Governance requirements in respect of the need for medical device approval for devices making a medical diagnosis ; Also the need to know the provenance of any sensors that you may wish to use This presentation discusses the issues of IoT when operating in a medically regulated environment, the potential benefits and the possible downfalls. The presentation will also touch upon the fact that IoT is often talked about in the same breath as 5G with its targeted High Spectral efficiency and high bandwidth capabilities as a means of providing the perceived connectivity needs. Yet most potential sensors and devices in an eHealth environment potentially require limited bandwidth so another question also touched upon is does IoT need 5G in the context of the eHealth environment

-

- A Dynamically Reconfigurable ECC Decoder Architecture for the next generation communication standards (5G, SDR and behond)

-

Cyrille Chavet (Université de Bretagne Sud & Lab-STICC, France); Philippe Coussy (Uniuversite de Bretagne-Sud / Lab-STICC, France)

The incoming communication standards (e.g. 5G, cognitive radio, SDR...) will be the origins of a deep revolution for the future of our widely connected world, with new communication scenarios, communications interoperability (e.g. wireless broadband, Internet of Things, Machine to Machine, Smart&Digital Factory...). As an example, contrary to 3G or 4G, the incoming 5G standard gathers several different radio signals (LTE-A, Wi-Fi/WISE…) in licensed or free bandwidth, in a combined heterogeneous and flexible network; also, in the defence and security domain, the advent of the Software Defined Radio (SDR) follows the operational logic of interoperability and cost-reductions to rationalise stocks of radio equipments, by implementing various waveforms on the same telecommunication equipment... This trend will be characterized by convergence of communication networks, melting several physical layers, several communication protocols (Wi-Fi, LTE, RFID tags...). This supposes to deal with several different channel codes, different consumption constraints, throughput targets...; in other words, this future world will be based on multiple radio (multi-RAT), allowing a dynamic adaptation in frequency, codes... and heterogeneous networks. In this context, channel decoding (i.e. FEC, Forward Error Correction) architecture is a critical element of such systems, since it impacts the quality of services (QoS), power consumption and the efficiency of radio resources usage. In order to limit the costs, either in terms of development cost or power consumption cost, an adaptive architecture that could deal with some (or all) of these applications/codes is extremely interesting. It also requires to be extensible (various throughput/latency targets) and flexible ECC architectures, i.e. supporting of several types of codes (turbo codes, LDPC, polar codes...) that can be changed dynamically during operation. However, the excellent performance of current FEC decoders comes at the expense of huge computational complexity. Hence, parallel architectures must be employed to speed up the decoding process and support required application throughputs. Moreover, several parameters such as scheduling, parallelism level, memory organization and network architecture need to be explored to tradeoff circuit area and performances. This requires the development of dedicated approaches to efficiently implement decoder architecture. In such implementation several Processing Elements (PEs) are used to obtain the required throughput. Memories are used to store different messages generated during the decoding process. These messages are written into and read out of the memories according to particular permutation defined by a permutation law. In order, to propose FEC decoder architectures that could meet the previous requirements, new architectural technologies must be explored. This contribution presents an innovative approach to design efficient, low-power, agile and dynamically reconfigurable ECC (Error Correction Codes) architectures in order to reduce the hardware cost and to support multiple standards with reduced memory footprint. In other words, our goal is to propose a single architecture that could be used to deal with all 5G communications and/or SDR and/or … for a minimized specialization overhead (hopefully for free). One of the problems, for example, is that such architectures suffer from memory access conflicts due to concurrent data accesses (from PEs to memories). This issue comes from the interleaving law in turbo-like codes or from the parity check matrix in LDPC. Different approaches have been developed to tackle this problem: definition of conflict-free data access orders, using dedicated hardware mechanisms to deal with conflicts at runtime, finding conflict free memory mappings at design time (off-chip) or more recently hybrid strategy that finds conflict free memory mappings on-chip at runtime. In parallel decoder architectures, design time approaches require storing into ROM the control words to drive the network and to address data memories for particular block length or/and interleaving law. So, in order to design flexible decoder architectures that support multiple block lengths and interleaving laws, multiple ROMs are needed which results in an important hardware overhead. Our proposed architecture is based on the implementation of a patented approach for FEC hardware architecture. Currently, it is clear that latency required to implement our algorithm is in compliance of existing telecommunication standards (4G LTE). However, the low architectural cost of our algorithm makes it suitable to embed on telecommunication and signal processing system for supporting multiple applications and standards (i.e. like in 5G, Cognitive Radio…).

-

- SOLDER - The OpenAirInterface Application Programming Interface for Schedulers using Carrier Aggregation

- Florian Kaltenberger (Eurecom)

Tactical Communications - How to Benefit from Commercial Technologies (download presentations here)

Session Chair: David Renaudeau (Thales)

NNEC maturity level 4 - Collaboration based on open 3GPP standards

Kennet Nomeland (Norwegian Defence Material Agency)

Netherlands vision on mobile networks

Kol ir. Jan van de Pol (KIXS)

Finland - Incentives and framing conditions for the military incumbent to adopt LSA

Topi Tuukkanen (Finnish Defence Research Agency)

Wireless Technologies - Building the 5G Evolution 2 (download presentations here)

Session Chair: Claude Belisle, NordiaSoft

- On the Duality Between State-Dependent Channels and Wiretap Channels

-

David Kibloff (Univ Lyon, INRIA, INSA Lyon, CITI, France); Samir M. Perlaza (INRIA, France); Guillaume Villemaud (Université de Lyon, INRIA, INSA-Lyon, CITI, France); Leonardo S. Cardoso (Université de Lyon & INRIA, INSA-Lyon, CITI-INRIA, France)

In this work, the duality between state-dependent channels with causal channel state information at the transmitter and wiretap channels is established, and the conditions required for this duality to hold are given. Under these conditions, it is shown that an achievable scheme for the state-dependent channel is also an achievable scheme for the wiretap channel. Thus, results obtained for one model are shown to hold for the other. Moreover, it is found that for certain wiretap state-dependent channels with causal channel state information at the transmitter, secrecy is naturally guaranteed by the code construction for the state-dependent channel without requiring any additional effort to combat the eavesdropper.

-

- Multi-standard OFDM transceiver for heterogeneous system-on-chips

-

Pascal Cotret (IETR, CentraleSupélec, France); Vipin Kizheppatt (Mahindra Ecole Centrale, India); Christophe Moy (CentraleSupelec/IETR, France)

The platform presented in this work emphasizes the use of software/hardware heterogeneous devices for flexible multi-RAT architectures. Hardware improvements are mainly focused on Dynamic Partial Reconfiguration (DPR) and especially reconfiguration speed. Management of the reconfiguration process is based on a Hierarchical and Distributed Cognitive Radio Architecture Management (HDCRAM). Some scenarios based on network centralized orders or power consumption decentral- ized orders will be explained. The demonstration is a baseband OFDM transceiver with some emulated white Gaussian noise channel. It functionnaly consists of three parts: a transmitter, a receiver, and an additive white Gaussian noise (AWGN) channel. The transmitter has two blocks: Mapping and Inverse Fast Fourier Transform (IFFT), and the receiver has also two corresponding blocks: Fast Fourier Transform (FFT) and Demapping. On the hardware point of view, the demonstration is implemented on a laptop and a Zynq platform (device including a hardcore processor and a FPGA).

-

- A Phase Aligned Multi-Channel RF System Example

-

Ryan Koehn (National Instruments & BEEcube, USA); David Squires (National Instruments, USA)

Phase Aligned Multi-Channel RF Systems are a critical element in several application areas, including radar, direction finding, and massive MIMO. As technology in these areas evolves, there is an ever-growing need for more bandwidth and higher channel counts. These increasingly demanding system requirements necessitate a solution with both advanced IO synchronization capabilities and massive real time signal processing capacity. By combing high performing NI PXI RF instruments with the new NI FPGA ATCA Module for real time signal processing, it's possible to create multi-channel phase aligned systems that satisfy the performance requirements of some of the most challenging applications. This presentation develops a typical set of requirements for a phase aligned system with several GHz of aggregate processing bandwidth. A system architecture is created which satisfies these requirements and a specific implementation of such a system using off the shelf NI PXI and ATCA equipment is shown. Experimental results of this system are then presented.

-

RFNoC Tutorial Part 1 (download presentations here)

RFNoC (RF Network on Chip): Bringing the Power of the FPGA to GNU Radio

-

Manuel Uhm (Ettus Research, a National Instruments Company, USA)

Note: This tutorial is two 90-min sessions. When developing software defined radio (SDR) platforms, the process is very different when the target is a general purpose processor (GPP) versus a FPGA based design. On GPP platforms, there are many powerful SDR suites, such as GNU Radio (GR), that provide a modular stream based processing infrastructure that allow the developer to focus on algorithm development. In these GPP SDR suites, the user is generally not required to be an expert in the low level infrastructure. Conversely, most FPGA platforms are monolithic implementations that require the user to be an expert in both their algorithm and the intimate details of the FPGA design's infrastructure. Furthermore, the FPGA platforms lack the GPP based SDR suite's ability to easily add, rearrange, and reconfigure processing blocks. However, FPGAs have tremendous parallel processing capability and can accelerate many SDR related algorithms. An ideal platform would allow heterogeneous processing with the GPP and FPGA while retaining the ease of design and flexibility of GPP based SDR. RF Network on Chip (RFNoC) is our implementation of such a platform. RFNoC is a new processing framework for Ettus Research third generation USRP devices that aims to make FPGA acceleration in SDR more accessible. RFNoC implements a packetized network infrastructure in the USRP's FPGA that handles the transport of control and sample data between the GPP and radio. Users implement their custom algorithms in FPGA based processing blocks, or Computation Engines (CEs), that attach to this network. CEs act as independent nodes on the network that can receive from and transmit data to any other node (such as another CE, radio frontend, or GPP.) This framework permits scalable designs that can distribute processing across many nodes. Users can create modular, FPGA accelerated SDR applications by chaining CEs into a flow graph in a fashion similar to many GPP SDR suites. One such suite, GNU Radio (GR), fully supports RFNoC. Users can create flow graphs containing both GR blocks and RFNoC CEs that seamlessly communicate. CE parameters, such as FFT size and FIR filter coefficients, can be set from within GNU Radio like any other GR block. By simplifying access to the FPGA, the same hardware can be more easily used for more demanding applications. We will present an in depth tutorial on RFNoC including a discussion on its design and capabilities, demos of several existing examples, and instructions on how to implement Computation Engines in RFNoC.

Tactical Communications 3 - Interoperability Changes (download presentations here)

Session Chair: David Renaudeau (Thales)

WINNF CC SCA Interoperability Project: Objectives and Status

David Renaudeau (Thales)

EW & Red Force Tracking

Dominique Merel (Thales)

WInnF CC SCA: Status on the Forum WG

Eric Nicollet (Thales)

RFNoC Tutorial Part 2 (download here)

- RFNoC (RF Network on Chip): Bringing the Power of the FPGA to GNU Radio

-

Manuel Uhm (Ettus Research, a National Instruments Company, USA)

Note: This tutorial is two 90-min sessions. When developing software defined radio (SDR) platforms, the process is very different when the target is a general purpose processor (GPP) versus a FPGA based design. On GPP platforms, there are many powerful SDR suites, such as GNU Radio (GR), that provide a modular stream based processing infrastructure that allow the developer to focus on algorithm development. In these GPP SDR suites, the user is generally not required to be an expert in the low level infrastructure. Conversely, most FPGA platforms are monolithic implementations that require the user to be an expert in both their algorithm and the intimate details of the FPGA design's infrastructure. Furthermore, the FPGA platforms lack the GPP based SDR suite's ability to easily add, rearrange, and reconfigure processing blocks. However, FPGAs have tremendous parallel processing capability and can accelerate many SDR related algorithms. An ideal platform would allow heterogeneous processing with the GPP and FPGA while retaining the ease of design and flexibility of GPP based SDR. RF Network on Chip (RFNoC) is our implementation of such a platform. RFNoC is a new processing framework for Ettus Research third generation USRP devices that aims to make FPGA acceleration in SDR more accessible. RFNoC implements a packetized network infrastructure in the USRP's FPGA that handles the transport of control and sample data between the GPP and radio. Users implement their custom algorithms in FPGA based processing blocks, or Computation Engines (CEs), that attach to this network. CEs act as independent nodes on the network that can receive from and transmit data to any other node (such as another CE, radio frontend, or GPP.) This framework permits scalable designs that can distribute processing across many nodes. Users can create modular, FPGA accelerated SDR applications by chaining CEs into a flow graph in a fashion similar to many GPP SDR suites. One such suite, GNU Radio (GR), fully supports RFNoC. Users can create flow graphs containing both GR blocks and RFNoC CEs that seamlessly communicate. CE parameters, such as FFT size and FIR filter coefficients, can be set from within GNU Radio like any other GR block. By simplifying access to the FPGA, the same hardware can be more easily used for more demanding applications. We will present an in depth tutorial on RFNoC including a discussion on its design and capabilities, demos of several existing examples, and instructions on how to implement Computation Engines in RFNoC.

Dynamic Spectrum - Military & Commercial Perspectives 1 (download presentations here)

Session Chair: David Renaudeau (Thales)

- NATO IST-140 RTG-065 Cognitive Radio Networks - Efficient Solutions for Routing, Topology Control, Data Transport, and Network Management

-

Stefan Couturier (Fraunhofer-Institut FKIE, Germany); Timo Bräysy (University of Oulu & Centre for Wireless Communications, Finland); Boyd Buchin (Rohde & Schwarz, Germany); Lorenza Giupponi (Centre Tecnològic de Telecomunicacions de Catalunya (CTTC), Spain); Jaroslaw Krygier (Military University of Technology, Poland); Vincent Le Nir (Royal Military Academy, Belgium); Topi Tuukkanen (Finnish Defence Research Agency, Finland); Erik Verheul (Royal Netherlands Navy, The Netherlands)

Cognitive Radio Networks is a topic of high relevance for both the civilian and the military world. According to literature, Cognitive Radio Networks are more than just a network of Cognitive Radios. While Cognitive Radios focus on finding the best frequencies to transmit messages to their neighbours (dynamic spectrum access), Cognitive Radio Networks aspire to transmit messages in the fastest, safest, and most efficient ways to their destinations (end-to-end optimization). Nevertheless, most of the current networking techniques have neither been designed for Cognitive Radio nor for military use. The ongoing NATO IST-140 research task group investigates challenges and solutions for Cognitive Radio Networks in a military context with regard to techniques like routing, topology control, network management, or exchange of control information. This presentation gives insights into the work of the group and its status.

- Cognitive Radio: Thoughts and Projects

Thierry Defaix (France DGA)

Coordinated Dynamic Spectrum Management in Legacy Military Communication Systems

Presenter TBA (Poland MUT, MCI)

An Overview of AFRL Topics for Spectrum Access Research & Development

Jonathan Ashdown, PhD (US Air Force Research Laboratory (AFRL))

France DGA Wireless Innovation Framework for Dual Applications 1 (download presentations here)

Session Chair: Jean Philippe Delahaye (DGA: Direction Générale de l’Armement)

- Introduction: France DGA Wirless Innovation Framework for Dual Applications

Presenter TBA -

- Enhanced air-ground communications in fast moving, multi-path environments

-

Olivier Rousset (Teamcast, France); Kevin Mille (Thales Communications & Security, France); Samuel Guillouard (TEAMCAST, France)

Air-ground communications in CAS (Close Air Support) applications are characterised by a fast moving transmitter (Aircraft) and a receiver sometimes located in an urban area, with many surrounding buildings acting as wave reflectors. In such situations, high speed data communications (e.g. for a video signal) using single carrier modulation are severely hampered by the echoes. Two French project associating the SME TeamCast and Thales Communications & Security have proposed enhancements for such applications. Both projects were supported by the French Ministry of Defence. The first project, ECHO, added an efficient channel equalizer on the receiver capable of cancelling echoes within a 5 µs time interval. This equalizer also handles high Doppler spread, up to 4 kHz, at the cost of sacrificing some net capacity by inserting reference patterns. The second project, MAXSIMO, added antenna diversity to the ECHO receiver in order to further improve the robustness of the transmission. In both projects, after proper channel models were defined, the algorithms were first refined through simulation, real-time demonstrators were built and the performances of the proposed solutions were verified through extensive laboratory testing using channel emulators. This presentation is about the results of the two projects. It shows the significant gains of transmission performance reached by the two complementary approaches.

-

- Waveform Recognition for SDR based Radio Intrusion test platforms

-

Fatima Zohra Kaddour (SILICOM - France); Habib B.A. Sidi (INRIA, France); Mehrez Selmi (SILICOM, France)

Programmable radio systems and low-cost devices with sufficient computational power have fostered the development of Software Defined Radio (SDR) which is experiencing a rapid growth. Since the SDR can change its function by changing the software, the hacking procedure could be developed without investing in expensive hardware or circuitry-making equipment. The objective of the TIRAD project is to develop an agile SDR platform to test radio intrusion and elaborate attacks on various wireless communication systems. The developed platform is based on existing tools from the GnuRadio project and low-cost devices such as Universal Software Radio Peripheral (USRP) N210. The main challenge in developing such system is the capability to detect and identify anonymous communications covering a large range of wireless communication technologies. Thus, the platform is based on a sniffing procedure that detects a wireless transmission and provides to the hacking procedure the main characteristics of the waveform. We focus on a semi blind recognition algorithm. This later is based on the constructed waveform ontology (i.e., data base) that contains the main characteristics of several wireless systems such as, the frequency bands, the modulation types or preambles. This recognition is based in three main steps: (i) spectrum analysis: this consists of a sniffing procedure that scans the frequency spectrum in order to detect an eventual transmission using the energy thresholding method and identify both the occupied frequency band and the carrier frequency. The bins averaging technique is considered in order to increase frequency detection accuracy and prevents false peaks errors. Hence, based on the frequency bands information and the waveform ontology, a subset of a standard candidate is selected. However, this may be insufficient to fully recognize the transmitted waveform. Therefore, the two additional steps are performed: (ii) synchronization: which consists of detecting the preambles of the standard candidates given in the ontology, and (iii) demodulation: that reads some frame fields such as start frame delimiters and comparing them with the pre-recorded information. At the end of each step the subset of candidate wireless standards is short-listed. Finally, upon executing these successive steps, the waveform recognition result is given and the characteristics of the transmitted signal are depicted. The hacking procedure can then exploit the recognized waveform information to perform attacks. In the framework of this project, two wireless communication systems are hacked: (i) WiFi: by emulating a virtual access point, and (ii) ZigBee: where On/Off messages are sent to smart home plugs.

-

COMET Project: The COMET RAPID project, a contribution to the Unified Component Model (UCM) OMG standard

Thomas Vergnaud and Olivier Hachet (Thales)

For more than a decade, component-based software engineering has been considered a key enabler to increase software reuse and reduce time to market. In particular, several companies have adopted component-based software engineering for embedded real time or critical system. Due to the domain constraints, these companies have built their own component model and associated frameworks or have made significant adaptations to existing standards like to the lightweight CORBA Component Model standardized from OMG. Considering this example, the use of the LwCCM in embedded applications can lead to an undesired memory and storage footprint with its mandatory dependency on CORBA, avoiding usage of alternative middleware implementations. Moreover, most of the existing other component models are usually defined with a specific underlying middleware and the associated execution semantic that do not fit all DRTE environments. COMET is a RAPID project executed by Thales and Prismtech. It stands for “COmponent Model for distributed, Embedded real Time systems” and aims at defining a multi-domain component framework for embedded systems. It has strongly influenced the UCM standardization for a simple, lightweight, middleware-agnostic, and flexible component model taking into account DRTE concerns like mastering memory, defining specific interaction patterns, introducing mechanism to master non-functional properties.

-

Dynamic Spectrum - Military & Commercial Perspectives 2 (download presentations here)

Session Chair: Claude Belisle (NordiaSoft)

WRC-15 Results and 2019 perspectives

Yvon Livran (Thales)

UK - Military License Exempt Spectrum – The Need and Challenges

Anil Shukla (Qinetiq)

LSA Pilots in France & Finland

Presenter TBA

- Analysis of sharing economy antecedents in the Citizens Broadband Radio Service

-

Seppo Yrjölä (Nokia Innovation Steering)

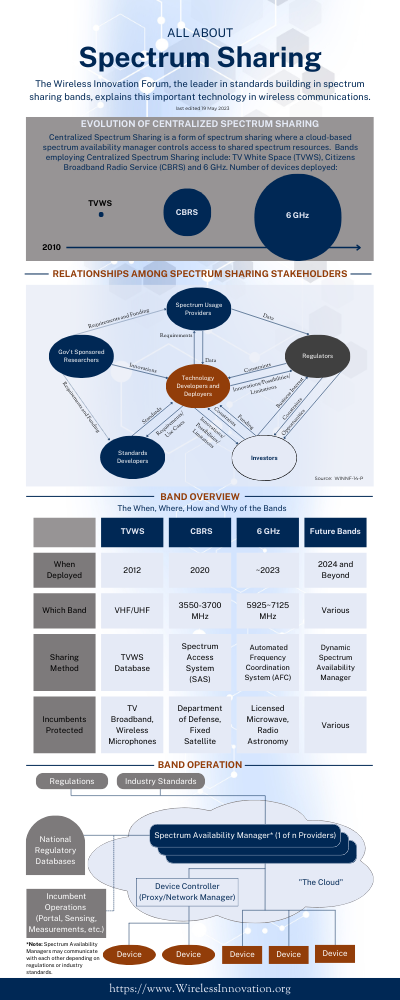

The exponential growth of wireless broadband services with diversity of devices and applications has inspired research community to come up with novel concepts to improve the efficiency of spectrum use. Recently several spectrum sharing system concepts have been introduced and widely studied to cope with spectrum scarcity, though to date only a few has developed into pre-commercial deployments. This paper discussed business model characteristics and sharing economy criteria of the spectrum sharing concepts, and evaluated the recent US Citizens Broadband Radio Service spectrum sharing concepts with respect to these criteria. For a spectrum sharing concept to be adopted it is essential not just to develop technology enablers to meet regulatory criteria but also to provide a scalable business model design for all the stakeholders. Harmonization and scalability of the platform and automation of processes will drive economies of scale and trigger early market opening. The model must be able to offer superior value proposition that offer access over ownership and ability to realize more choices with lower initial transactions costs compared to exclusive models. Value of the shared spectrum resources are highly dependent on its availability, liquidity and the predictability. Access and deployment of the underutilized assets on-demand is essential to generate continuous revenue early. Scalability of all sharing concepts could be highly impacted by fragmented national incumbent use cases, related different incumbent protection mechanisms and regulatory differences. Trust is the trigger of all collaborative shared consumption that makes system grow and scale. The creation of a critical mass ecosystem with positive network effects is important for all three approaches with new database spectrum administrator and broker roles. Simplicity of the offer built around user knowledge driven 'demand pull' is critical in value differentiation for existing services as well as in scaling new spectrum sharing enabled services. The analysis indicates that particularly the opportunistic third tier of the CBRS concept lowers entry barrier to new alternative operators, scale out ecosystem with new roles and foster service innovation particularly. On the other hand, introduced dynamism will increase system complexity, and requires novel technology enablers in building trust and ensuring pragmatic predictability in the spectrum management platform. The Sharing Economy provides a dynamic framework for analyzing and developing the spectrum sharing business models.

France DGA Wireless Innovation Framework for Dual Applications 2 (download presentations here)

Session Chair: Jean Philippe Delahaye (DGA: Direction Générale de l’Armement)

- Architectural exploration of a flexible and low-power Software Defined Radio

- Baptiste Roux1, Matthieu Gautier1, Jean-Philippe Delahaye2 and Olivier Sentieys1 (1 INRIA, University of Rennes 1, IRISA, France, 2 DGA-MI, France)

Software Defined Radio (SDR) systems are nowadays facing conflicting challenges. SDR systems historically deal with flexibility and throughput specifications by using either rapid prototyping or high computation power platforms. A new challenge appears while SDR platforms need to decrease their power consumption to achieve the same energy efficiency as specialized hardware. To tackle theses issues, the use of Multi-processor System-on-Chip (MpSoC) was investigated allowing a gain at both computation power capability and energy consumption levels. Furthermore, these architectures were recently extended with specialized accelerators, such as Field-Programmable Gate Array (FPGA) or Application-Specific Integrated Circuit (ASIC). Thus, Heterogeneous MpSoC (HMpSoC) appeared. This new kind of architecture introduces complex and hard-to-solved issues on software/hardware partitioning and task mapping, and leads to a huge design space. Furthermore, when energy consumption is a key requirement of the application, this solution space must be explored with a fast and accurate power estimation tool. Power modeling of MpSoC is not a new topic but state-of-the-art power estimation tools need a complete simulation of the application to achieve a high precision. Therefore they cannot be directly applied to task mapping process when HMpSoC architectures are targeted. Thus, two challenges must be tackled. First a fast power modelling tool is required to compute the power consumption for each mapping solution with no extra development delay. Then state-of-the-art design flows need to be modified to propose the best energy efficiency solution for a given throughput. The target heterogeneity must be efficiently managed by integrating a power modelling tool in the design flow. To answer the above challenges, our work introduces a communication-based power model that addresses a wide range of heterogeneous architectures. Our methodology is based on micro-benchmarking to estimate the model parameters. The energy model mainly relies on the energy overheads induced by communications between processors in a parallel application. Power modelling and micro-benchmarks are validated using a Zynq-based heterogeneous architecture showing the accuracy of the model for several tested synthetic applications. Our ongoing work targets the integration of this model in a full design flow to automatize the design space exploration with an energy-aware approach. The main objectives of this design flow are to ease the SDR application prototyping and to enable better energy performance.

-

- RF and digital architectures for VHF/UHF radio equipment

-

Matthieu Pastore (Telerad, France); Adrien Tuffery (TELERAD, France)

Standard VHF voice communications have not evolved much since their introduction in the first half of 20th century. For aircraft communications, we have been using the same modulation scheme since 1940. However, several trends have emerged in order to modernize this protocol which means that, increasingly, new waveforms have to be included in radio equipment while still supporting the standard A3E waveform, both for security and operational reasons. These include F3E/G3E in marine communications, ACARS and VDL2, 3 or 4 for data transmission, etc. Military users in particular need to cooperate with different civilian and military organizations and they have a thus a greater need of flexibility. Many different protocols or waveforms need to be supported into their radio units; civilian air and marine protocols, military OTAN and national protocols. It means that more than a dozen different waveforms would have to be included in one piece of radio equipment. In recent years, consumer electronics have substantially evolved and we now have many electronic components that are both cheap and performing well, especially for radio front-end. One of our challenges is to integrate these consumer technologies to lower costs, while still being able to guaranty a long term support guarantees (between 20 and 40 years) and good climatic performance In this presentation, we present our latest findings in order to address these challenges for VHF and UHF radios. There are two main topics: a new electronically tunable cavity filter for VHF and UHF radio bands, and new digital architectures both for transmission and reception functions. Part of the 3G RAPID project led by TELERAD was to develop innovative architectures for the RF front end of the receiver to obtain high selectivity, high linearity and cover a frequency wideband (108MHz to 512MHz). These still had to meet the requirements of military applications and also reduce the design costs when compared with state of the art architectures. In the VHF and UHF frequency ranges, high selectivity cannot be achieved with conventional topology implementing only discrete components or transmission line resonators. Hence tunable bandpass cavities are the best choice in order to obtain high selectivity in the targeted frequency range (108MHz-512MHz). In the first part of this presentation, we introduce a new architecture where traditional components, which have either limited linearity performances or a complex control circuit, are replaced by BST (Barium Strontium Titanate) capacitors which provide an electronic tuning for the cavity filter. In the second part, we will focus on new digital architectures for both transmission and reception functions. The goal is to both improve flexibility and reduce costs by integrating more and more analog functions into digital components. With regards to the transmission functions (work still being finalized), a new digital feedback control system has been studied which has two main benefits. Digital integration enables a better and easier tuning of VHF and UHF Power Amplifiers (PA) to cope with the extremely wide RF bandwidth (108-512MHz) and all the impairments associated with it. It also proves to be more flexible which allows better handling of disparate bandwidths and dynamic ranges (crest factor, or peak power in A3E) depending on the selected waveforms. With regards to reception functions, a new hybrid "direct IF" conversion function has been studied, with similar benefits. The algorithms and architectures developed there are not particularly "brand new", but adapting them to VHF/UHF radio bands can be difficult and poses different challenges and trade-offs, all of which will be discussed in more detail. Acknowledgements: This work has been supported by the DGA RAPID project "Radio3G - Modules émission et réception large bande pour radio logicielle TELERAD 3G"

-

- Implementation of the Radio Frequency IDentification (RFID) technology in the Software Defined Radio (SDR)

-

Frédéric Le Roy (ENSTA Bretagne, France)

Several applications and services such as national identification cards, passports and credit cards had been recently introduced as an implementation of the Radio Frequency IDentification (RFID) technology in the Software Defined Radio (SDR) context. In this work, we will investigate the faisability of these ISO/IEC 14443 RFID B waveform implementation on low cost or high speed SDR platforms. We will study different timing modes of the WInnF Transceiver Facility (Transceiver API) specifications and will focus on the impact of these considerations on different platforms using different frameworks. We will then try to describe a measurement testbench for a low cost SDR platform associated to the better timing mode.

ACM Project : Accelerating Code from Matlab

Philippe Ravier (Silkan)

We shall present the most recent breakthrough achieved by COLDTM within ACM, an ongoing project supported by a DGA/RAPID grant. COLDTM is a compiler which automatically turns MATLAB®/Scilab programs into highly effective parallel runtimes, thus allowing a noticeable increase in productivity by avoiding the delay and cost incurred when high performance implementation is required to allow to a realistic TRL validation of the applications in view. We shall present the underlying technology, demonstrate representative performance results, and conclude by sketching further developments currently in progress or foreseen in the near future.

SDR Standards and Waveform Portability 1 (download presentations here)

Session Chair: Sarvpreet Singh (Fraunhofer-Institut)

- A Single Design Environment for SDR & CR Development

-

Manuel Uhm (Ettus Research, a National Instruments Company, USA)

Waveform development and porting continues to be a significant barrier to adoption and deployment of SDRs and cognitive radios, which is why it is #1 on the list of Top 10 Innovations desired by the Wireless Innovation Forum. A big part of the problem is that most SDRs have heterogeneous processors (typically an FPGA and GPP) with independent tool flows. This makes both design and debug of SDRs challenging. It is far preferable to have a single design environment that encompasses all the processors in the system, regardless of the type of processor. The USRP(tm) family of SDRs actually offers two independent design environments that meet this requirement: 1) Ettus Research USRPs (3rd generation) which offer an open source single design environment via GNU Radio Companion and RFNoC(tm), and 2) National Instruments USRPs which offer an easy-to-use single design environment via the integration of LabVIEW and LabVIEW FPGA. Both tool flows have their respective pros and cons but they both offer a single design environment to ease the development of SDRs and CRs.

-

- Increasing Performances of SCA Applications that use OpenCL

-

François Levesque, Steve Bernier and Martin Phisel (NordiaSoft, Canada); David Hagood (Cobham, USA)

Open Computing Language (OpenCL) can be used in conjunction with the SCA to build more portable applications that execute across heterogeneous platforms consisting of GPPs, DSPs, FPGAs, and graphics processing units (GPUs). This paper starts with an overview of how SCA components can be built using OpenCL. It compares the results of performance metrics of an application implemented as a single OpenCL-SCA component with the results for the same application implemented as several OpenCL-SCA components. The paper provides a detailed discussion on how the data buffers being processed flow in and out of the OpenCL target memory and demonstrates how the flow affects performances. A novel approach is proposed to minimize the amount of data movement across the communication bus between different computing devices. The paper concludes on performance metrics characterizing the new approach.

- Improving portability for radio signal processing layers: the Transceiver Test Tool

-

Jean-Julien Sabiani and Frédéric Bruel (Thales, France); Frederic Lafaye (Thales); Eric Nicollet (Thales, France)

Portability of radio signal processing SDR Application layers requires to ensure consistency between the developed SDR Application and the underlying radio signal acquisition system on much more than the API software interface. Standard Transceiver APIs (from WInnF and ESSOR) have therefore augmented the traditional software interface standardization ("API" strictly speaking) with the concept of Performance Criteria, that address the complementary areas of signal processing performance, time accuracy of over-the-air bursts operation and hard real-time programming constraints. Verifying that a given Transceiver implementation meets the requirements of the signal processing SDR Application layer has become a critical aspect on the IVV path, which led to development of the Thales Transceiver Test Tool. The Transceiver Test Tool, stemming from earlier portability experiences, developed and used in ESSOR Programme, is now used in on-going SDR products developments. It enables to secure porting of Thales waveform PHY Layers. Presentation will describe the Transceiver test Tool, share lessons learnt and considerations on further uses and possible evolutions.

-

Design and Implementation of a MAC-PHY-API for better waveform portability

Robert Koch (Fraunhofer IIS), Martin Kohlmann (Fraunhofer IIS), Ewald Hedrich (Fraunhofer IIS), Jochen Martin-Creuzburg (Fraunhofer Institute for Integrated Circuits IIS), Christoph Barz (Fraunhofer FKIE), Henning Rogge (Fraunhofer Inst. for Communication, Information Processing and Ergonomics FKIE), Marc Adrat (Fraunhofer FKIE / KOM)

Waveform development, implementation, test and portability can be significantly improved with the aid of carefully designed interfaces between the big functional layers like transceiver subsystem, PHY, MAC or Link layer. In a Software defined Radio (SDR) these interfaces are provided by APIs. The Wireless Innovation Forum is amongst others well known for its work on the "transceiver facility" API. The Fraunhofer Institutes IIS and FKIE are working together with the German BAAINBw on the prototypal implementation and testing of a flexible, scalable and networking capable waveform for the tactical domain (VHF and lower UHF). The first spiral of the waveform was demonstrated at 2016 CWIX at JFTC in Poland. Besides the pure implementation of the waveform, focus is also on the design of powerful interfaces between the layers, to support the overall idea of rapid prototyping for the current requirements and the extension of single modules without touching the whole system. The design of a MAC-PHY-API clearly separates the sample driven and highly mathematical signal processing of the physical layer implementation from the timing driven data burst transmission of the higher layers that is controlled by the MAC protocol. Therefore the physical layer hides all the modulation details to the higher layers and provides a functional interface for transmitting and receiving bursts of different length and with different modulation and coding schemes. The MAC layer in turn calculates the expected point in time where the signal shall be on air, corresponding to the timing scheme implemented. Therefore all timing information inside the SDR is well known and related to the actual transmission or reception of a single sample at the antenna of the radio. The timing information is propagated from the antenna to the physical layer on the basis of samples. After the demodulation of a receiving burst the timing information is propagated to the MAC layer in terms of the relative SDR's clock, e.g. as a value in nano-seconds since system startup. All lower level signal processing and even the system's actual sample rate are concealed to the higher layers and all MAC scheme operations can be computed as (relative) units of time. With the presentation at the Wireless Innovation Forum we want to show the currently ongoing work of our project and we are interested in sharing experiences of other participants regarding the design of waveform APIs.

SDR Standards and Waveform Portability 2 (download presentations here)

Session Chair: David Renaudeau (Thales)

- Defining and using Standard Transceiver APIs: 10 years of lessons learnt

-

Eric Nicollet (Thales, France)

The presentation will share 10 years of lessons learnt in various efforts aimed at definition and usage of standard Transceiver APIs. Definition aspects will namely refer to: the PEA AL; the CP277 submitted in 2005 for SCA 3.0; the response to the OMG Digital IF RFP; the WInnF Transceiver Facility V1; the ESSOR Transceiver API; the WInnF Transceiver Next project. Usage reports will be based on: the PEA AL, WINTSEC, ESSOR studies, plus stories taken from products development experiences.

- SDR Application portability: experiences and perspectives

-

Eric Nicollet, Yves-André Caparros, Jean-Julien Sabiani and Frédéric Dotto (Thales, France)

Encompassing the whole range of waveform capabilties, from Protocol layers down to PHysical layers, the presentation will share perpectives from Thales development teams regarding porting experiences and perspectives. The discussion is taking the ESSOR Porting Methodology as basis for discussion, grounded on the ESSOR and on-going development experiences. Concept, benefit and practices attached to the concept of Base Waveform are given particular attention.

EDA Perspective on SDR standards

Philippe Cambraye (EDA)

- ETSI Reconfigurable Radio Systems (RRS) role and activies

Markus Mueck (Intel)

The Wireless Innovation Forum does not endorse or recommend the content of any of papers and presentations contained within these proceedings, rather these items are listed strictly as a service for the community. The information and materials contained in these proceedings are provided "as is" without warranty of any kind, either express or implied, including without limitation, any warranty of accuracy, adequacy or completeness of the information and materials, title, non-infringement of third party rights, merchantability, fitness for a particular purpose, etc.

|